low - Jitter , One to Four PLL Devices Ease Design para Consumer Applications

DALLAS ( 10 de julio de 2007 ) - Texas Instruments ( TI ) ( NYSE : TXN ) today introduced family of highly - programmable , 1 a 4 phase - lock loop ( PLL ) clock generator devices with ability generate up to 9 output clock sources from a single input frequency . Cada salida puede ser programado en el sistema para cualquier frecuencia de reloj 230 MHz. Estas características proporcionan una serie de beneficios para el sistema como menor consumo de energía, menor tiempo de plomo y la flexibilidad necesaria para actualizar fácilmente el reloj sin tener que rediseñar el sistema. Estos beneficios en última instancia, reducen los costos para una amplia gama de aplicaciones de consumo como IP set-top box o teléfonos, sistemas de medios digitales, como los televisores digitales, streaming de medios de comunicación y las impresoras, sistemas de navegación y dispositivos portátiles. (Consulte www.TI.com/CDCE949-PR .)

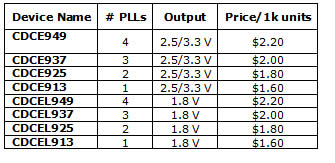

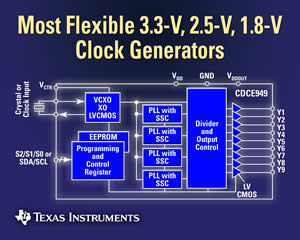

La nueva familia de CDCE9xx y CDCEL9xx de los generadores de reloj oscila entre uno y cuatro PLL con muy baja vibración en 60 nanosegundos típicos. Los dispositivos de CDCE9xx proporcionan salidas de 2,5 V o 3,3 V, y la CDCEL9xx proporcionan salidas de 1,8 V, lo que permite la capacidad de bajo consumo de energía necesaria para dispositivos portátiles. Cada PLL admite espectro ensanchado de sincronización (SSC) para reducir las interferencias electromagnéticas (EMI) para facilitar el cumplimiento con regulaciones de EMC.

La familia ofrece una variedad de opciones de programación, incluida la capacidad de programar y personalizar los dispositivos en el sistema a través de I2C y EEPROM. Ofreciendo compatibilidad de espacio a toda la familia, los diseñadores pueden adaptar el diseño del sistema fácilmente sin cambiar el hardware, lo que reduce los costos y permite al diseñador simplemente aumentar o disminuir el número de salidas de reloj. La nueva familia de dispositivos más simplifica el diseño de sistema mediante el reemplazo de un número de componentes en el sistema, incluidos los cristales, osciladores, buffers y PLL.

Los nuevos dispositivos de reloj están optimizados para trabajar con TI DaVinci TM -los procesadores basados en mediante la generación de cualquier reloj audio, vídeo, procesador o interfaz para impulsar el procesador digital, el convertidor de audio digital a analógico o el códec y el controlador de Ethernet o USB. El oscilador de cristal controlados por tensión de on-chip (VCXO) permite la sincronización de la frecuencia de diferentes flujos de datos.

TI proporciona una amplia selección de dispositivos de soporte, tanto PLL basados y no-PLL-, para apoyar al consumidor, las comunicaciones y aplicaciones de memoria de temporización. Información sobre la línea completa de productos de reloj de TI se encuentra en los relojes y la Guía de selección de alarmas, disponible en www.TI.com/Clocks .

Nueva familia de generador de reloj

La nueva familia de CDCE9xx y CDCEL9xx de los generadores de reloj oscila entre uno y cuatro PLL con muy baja vibración en 60 nanosegundos típicos. Los dispositivos de CDCE9xx proporcionan salidas de 2,5 V o 3,3 V, y la CDCEL9xx proporcionan salidas de 1,8 V, lo que permite la capacidad de bajo consumo de energía necesaria para dispositivos portátiles. Cada PLL admite espectro ensanchado de sincronización (SSC) para reducir las interferencias electromagnéticas (EMI) para facilitar el cumplimiento con regulaciones de EMC.

La familia ofrece una variedad de opciones de programación, incluida la capacidad de programar y personalizar los dispositivos en el sistema a través de I2C y EEPROM. Ofreciendo compatibilidad de espacio a toda la familia, los diseñadores pueden adaptar el diseño del sistema fácilmente sin cambiar el hardware, lo que reduce los costos y permite al diseñador simplemente aumentar o disminuir el número de salidas de reloj. La nueva familia de dispositivos más simplifica el diseño de sistema mediante el reemplazo de un número de componentes en el sistema, incluidos los cristales, osciladores, buffers y PLL.

Los nuevos dispositivos de reloj están optimizados para trabajar con TI DaVinci TM -los procesadores basados en mediante la generación de cualquier reloj audio, vídeo, procesador o interfaz para impulsar el procesador digital, el convertidor de audio digital a analógico o el códec y el controlador de Ethernet o USB. El oscilador de cristal controlados por tensión de on-chip (VCXO) permite la sincronización de la frecuencia de diferentes flujos de datos.

TI proporciona una amplia selección de dispositivos de soporte, tanto PLL basados y no-PLL-, para apoyar al consumidor, las comunicaciones y aplicaciones de memoria de temporización. Información sobre la línea completa de productos de reloj de TI se encuentra en los relojes y la Guía de selección de alarmas, disponible en www.TI.com/Clocks .

Nueva familia de generador de reloj

Disponibilidad

El CDCE949 ahora está disponible en paquete TSSOP de 24 pines. Los dispositivos restantes en la familia estará disponibles a lo largo de 2007 en paquetes TSSOP de 20 pines, 16- y 14 pines. Además, mo de evaluación